# **Intel<sup>®</sup> Atom™ Processor C2000 Product Family for Microserver**

**Datasheet**

January 2016

Order Number: 330061-003US

By using this document, in addition to any agreements you have with Intel, you accept the terms set forth below.

You may not use or facilitate the use of this document in connection with any infringement or other legal analysis concerning Intel products described herein. You agree to grant Intel a non-exclusive, royalty-free license to any patent claim thereafter drafted which includes subject matter disclosed herein.

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

A "Mission Critical Application" is any application in which failure of the Intel Product could result, directly or indirectly, in personal injury or death. SHOULD YOU PURCHASE OR USE INTEL'S PRODUCTS FOR ANY SUCH MISSION CRITICAL APPLICATION, YOU SHALL INDEMNIFY AND HOLD INTEL AND ITS SUBSIDIARIES, SUBCONTRACTORS AND AFFILIATES, AND THE DIRECTORS, OFFICERS, AND EMPLOYEES OF EACH, HARMLESS AGAINST ALL CLAIMS COSTS, DAMAGES, AND EXPENSES AND REASONABLE ATTORNEYS' FEES ARISING OUT OF, DIRECTLY OR INDIRECTLY, ANY CLAIM OF PRODUCT LIABILITY, PERSONAL INJURY, OR DEATH ARISING IN ANY WAY OUT OF SUCH MISSION CRITICAL APPLICATION, WHETHER OR NOT INTEL OR ITS SUBCONTRACTOR WAS NEGLIGENT IN THE DESIGN, MANUFACTURE, OR WARNING OF THE INTEL PRODUCT OR ANY OF ITS PARTS.

Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The information here is subject to change without notice. Do not finalize a design with this information

The products described in this document may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Intel literature, may be obtained by calling 1-800-548-4725, or go to:  $http://www.intel.com/\#/en_US_01$

January 2016

Order Number: 330061-003US

Intel, the Intel logo, Intel Atom, Intel Atom Inside, Intel Core, Intel Inside, Intel Insider, the Intel Inside logo, Intel, Intel SpeedStep, and Xeon are trademarks of Intel Corporation in the U.S. and/or other countries.

\*Other names and brands may be claimed as the property of others.

Copyright  $\ensuremath{@}$  2016, Intel Corporation. All rights reserved.

### **Revision History**

| Date           | Revision | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| January 2016   | 003US    | The following technical changes were made in Datasheet 003US:  Table 1-2 - Added "Lowest Frequency Mode" row to table and removed "Reliability/ Availability" row from table.  Table 1-4 - Added CPPM to terminology.  Section 3.3.1 and Section 3.3.2 - Corrected minimum memory capacity, and device density.  Table 3-1 and Table 3-2 - Added row for 1 GB.  Section 3.4.2 - Added Paragraph.  Section 4.4 - Updated section.  Table 5-2 - Updated signals.  Section 7 - Added note to SoC Reset and Power Supply Sequences.  Section 7.1.3 - Changed sequence shown in V1P0A voltage is provided to all V1P0A voltage-group pins the of SoC.  Section 7.2.1 - Updated Cold Reset Sequence.  Section 12.3.6 - Added note.  Section 12.3.6 - Added note.  Section 12.4.7.1 and Section 15.4.8.1- Updated.  Table 22-3 - Updated entries in Content column.  Section 22.7 - Added note.  Table 23-2 - Updated descriptions.  Table 25-1 - Updated and clarified reserved bits in Section 25.3.1.  Figure 31-1 and Table 31-14 - Updated signal names.  Table 31-15 - Updated RTC Well Signals.  Table 31-17 - Updated Description of PMU_RESETBUTTON_B/GPIOS_30.  Table 31-24 - Updated entries in "Internal Pull-up or Pull-down" column.  Table 31-25 - Updated entries in "Internal Pull-up or Pull-down" column.  Table 31-25 - Updated entries in "Internal Pull-up or Pull-down" column.  Table 33-2 and Table 33-3 - Updated signal name of TDQS_CK.  Table 33-42 - Updated RTC Crystal Requirements.  Figure 33-10 - Figure updated. |

| September 2014 | 002US    | The following technical changes were made in Datasheet 002US:  Updated Revision numbering scheme for public release from 1.1 to 002US.  Global Change - IRERR changed to IERR throughout the manual.  Global Change - SMBALERT# changed to SMBALRT_N throughout the manual.  Table 1-2 - Added CUNIT_REG_DEVICEID[31:0] row.  Section 3.3.3 - Added System Memory Technology which is Not Supported.  Table 3-2 - Added Table note.  Section 7.2.1 - Updated V1P35S note.  Section 9.3 - Updated PCI Express.  Section 11.5.2.1 - Added paragraph.  Table 12-2 - Updated Description for FLEX_CLK_SE1.  Section 12.2 - Updated Sypported features.  Section 12.2 - Updated ASPM and ASPM Optionality.  Section 12.6 - Updated Power Management.  Table 12-9 - Added x4 Lanes with 4 Controllers SKUs.  Previous Section 16.5.2 - Deleted section.  Table 16-1 - Changed Strap Usage for FLEX_CLK_SE1.  Table 16-5 - Updated Description for Bits 1 and 0.  Table 17-4 - Added Table Note 1 to Slave Address (Data Phase).  Table 31-6 - Updated Description for THERMTRIP_N.  Table 31-24 - Changed FLEX_CLK_SE1 pin 0 to Reserved.  Section 33.16.4 - Changed PPM Tolerance to 35 ppm.  Table 33-45 - Changed TRISE/FALL Min and Max Rise/Fall Time Max from 5ns to 3ns.                                                                                                                                                                                                                                                                     |

| January 2014   | 1.0      | Initial Release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

Intel  $^{\circledR}$  Atom  $^{\intercal}$  Processor C2000 Product Family for Microserver Datasheet \$3\$January 2016 Order Number: 330061-003US

## Contents

| Vol | ume   | 1: C2000 Product Family Program Overview                          | 30       |

|-----|-------|-------------------------------------------------------------------|----------|

| 1   |       | oduction and Product Offerings                                    |          |

|     | 1.1   | Overview                                                          |          |

|     | 1.2   | Key Features                                                      | 32       |

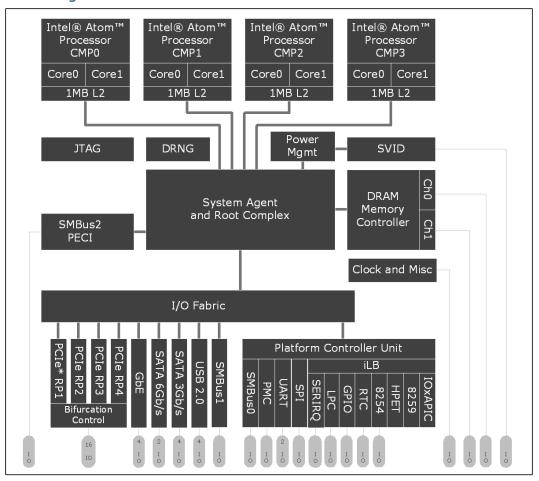

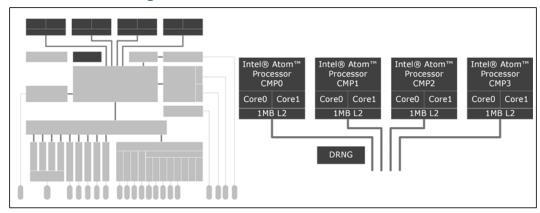

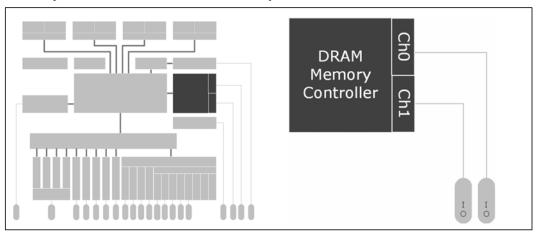

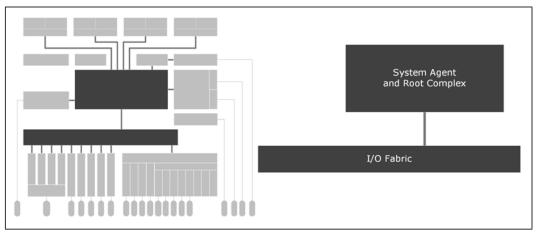

|     | 1.3   | Intel® Atom™ Processor C2000 Product Family for Microserver Block | 2.4      |

|     | 1.4   | Diagram                                                           | 34       |

|     | 1.5   | Datasheet Volume Structure and Scope                              |          |

|     | 1.6   | Terminology                                                       |          |

|     | 1.7   | Related Documents                                                 |          |

| 2   | Multi | i-Core Intel <sup>®</sup> Atom™ Processors                        | 46       |

|     | 2.1   | Signal Descriptions                                               | 46       |

|     | 2.2   | Features                                                          | 46       |

|     | 2.3   | SoC Components                                                    | 47       |

|     |       | 2.3.1 SoC Core                                                    |          |

|     | 2.4   | Features                                                          |          |

|     |       | 2.4.1 Intel® Virtualization Technology                            |          |

|     |       | 2.4.2 Intel® VT-x Objectives                                      | 48       |

|     |       | 2.4.2.1 Intel® VT-x Features                                      |          |

|     |       | 2.4.3 Security and Cryptography Technologies                      |          |

|     |       | 2.4.3.1 Advanced Encryption Standard New Instructions (AES-NI)    |          |

|     |       | 2.4.3.2 PCLMULQDQ Instruction                                     |          |

|     |       | 2.4.3.3 Digital Random Number Generator                           |          |

|     |       | 2.4.4.1 Intel® Turbo Boost Technology Frequency                   |          |

|     | 2.5   | CPUID Instruction and SoC Identification                          |          |

| Vol |       | 2: Functional                                                     |          |

| 3   |       | ory Controller                                                    |          |

| 3   | 3.1   | Introduction                                                      |          |

|     | 3.1   | Signal Descriptions                                               |          |

|     | 3.3   | Features                                                          |          |

|     | 5.5   | 3.3.1 Supported Memory Configuration                              |          |

|     |       | 3.3.2 System Memory Technology Supported                          |          |

|     |       | 3.3.3 System Memory Technology which is Not Supported             | 50<br>59 |

|     | 3.4   | RAS Features                                                      | 60       |

|     |       | 3.4.1 Data Parity Protection                                      |          |

|     |       | 3.4.2 Memory Controller Error Correcting Codes (ECC)              |          |

|     |       | 3.4.3 Demand and Patrol Scrubbing                                 |          |

|     |       | 3.4.4 DDR3 Data Scrambling                                        | 62       |

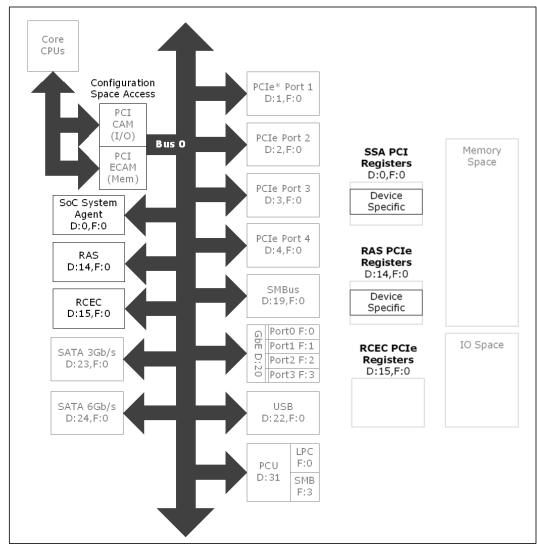

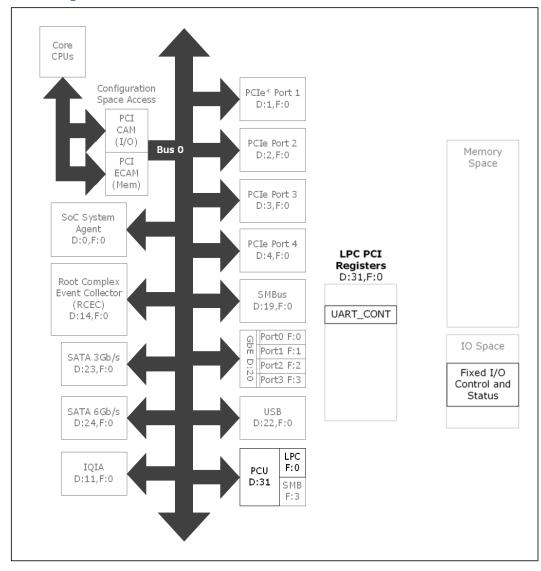

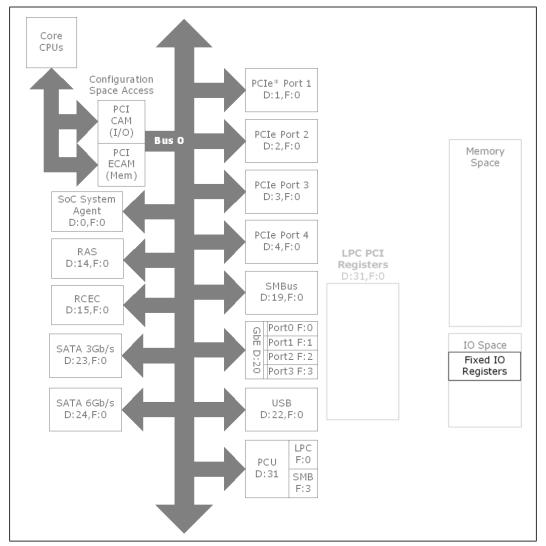

| 4   | Syste | em Agent and Root Complex                                         | 63       |

|     | 4.1   | Introduction                                                      |          |

|     | 4.2   | Signal Descriptions                                               |          |

|     | 4.3   | Features                                                          |          |

|     | 4.4   | Root Complex                                                      |          |

|     |       | 4.4.1 Transaction Flow                                            |          |

|     |       | 4.4.2 Root Complex Primary Transaction Routing                    |          |

|     | 4.5   | Reliability, Availability and Serviceability (RAS)                |          |

|     | 4.6   | Error Classification                                              | 68       |

|     |       | 4 b i correctable errors                                          | nЧ       |

|   |                                                               | 4.6.2                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                              |

|---|---------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

|   |                                                               | 4.6.3                                                                                                                                          | Non-Fatal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Errors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                              |

|   |                                                               |                                                                                                                                                | 4.6.3.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Software Correctable Errors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 69                                                                                                         |

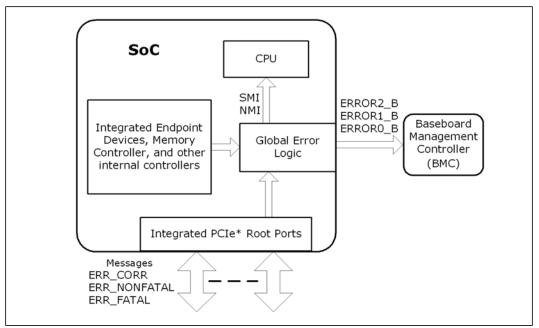

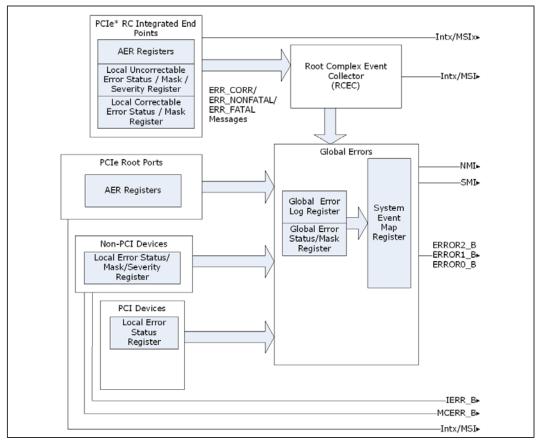

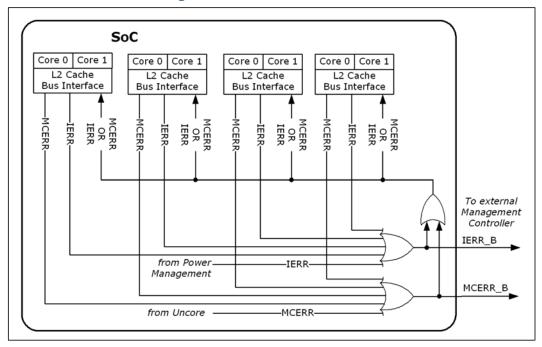

|   | 4.7                                                           | Global E                                                                                                                                       | Error Reporti                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | .70                                                                                                          |

|   |                                                               | 4.7.1                                                                                                                                          | Reporting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Errors to CPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | .72                                                                                                          |

|   |                                                               |                                                                                                                                                | 4.7.1.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Non-Maskable Interrupt (NMI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                              |

|   |                                                               |                                                                                                                                                | 4.7.1.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | System Management Interrupt (SMI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                              |

|   |                                                               | 4.7.2                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Global Errors to an External Device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                              |

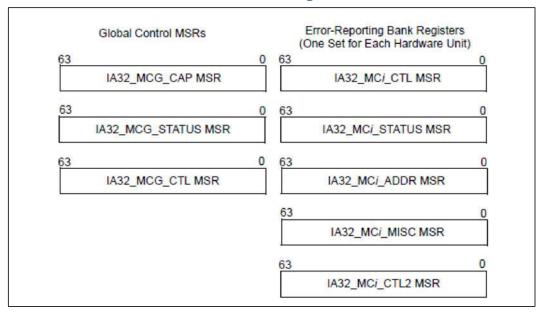

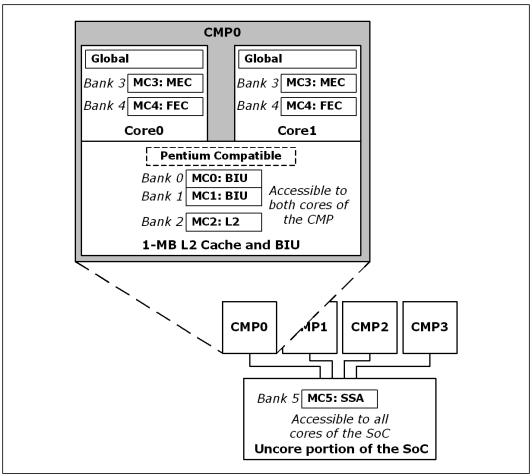

|   |                                                               | 4.7.3                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | heck Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                              |

|   |                                                               | т.7.5                                                                                                                                          | 4.7.3.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Machine Check Availability and Discovery                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                              |

|   |                                                               |                                                                                                                                                | 4.7.3.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | P5 Compatibility MSRs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 75                                                                                                           |

|   |                                                               |                                                                                                                                                | 4.7.3.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Machine Check Global Control MSRs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 76                                                                                                           |

|   |                                                               |                                                                                                                                                | 4.7.3.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Machine Check Error-Reporting MSR Banks 0-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 77                                                                                                           |